Understanding AHB OK: A Comprehensive Guide

AMBA High-performance Bus (AHB) is a crucial component in System on Chip (SoC) design, enabling efficient communication between various system components. In this article, we delve into the intricacies of AHB, focusing on its operation, features, and applications. Let’s explore the world of AHB OK in detail.

What is AHB?

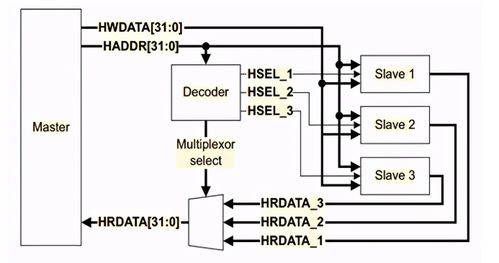

AHB is an interface bus protocol developed by ARM for connecting multiple components within a System on Chip (SoC). It facilitates high-speed data transfer between processors, memory, and I/O controllers, ensuring optimal system performance.

Key Characteristics of AHB

1. High Performance: AHB operates at high speeds, allowing for faster data transfer and improved system throughput. This is achieved through its ability to run at several hundred MHz, reducing the number of clock cycles required for data transmission.

2. Support for DMA and Hardware Data Translation: AHB supports Direct Memory Access (DMA) operations and hardware data translation, offloading the CPU’s workload and accelerating data transfer.

3. Isolation of Address and Data Signals: AHB uses separate address and data signals, ensuring high-speed transmission between the processor and memory without interference from other system activities.

4. Multi-cycle Operations: AHB supports multi-cycle operations, allowing for the completion of various operations over multiple clock cycles, enhancing its adaptability and flexibility.

Applications of AHB

1. Embedded Processors and Peripherals: AHB is widely used for data transmission between advanced embedded processors and peripherals, such as sensors, cameras, and communication interfaces.

2. Memory Interconnects: AHB facilitates efficient data transfer between different types of memory, including RAM, ROM, and flash memory.

3. System Design Flexibility: AHB provides designers with greater flexibility in building efficient and reliable SoC systems, as it allows for the integration of various high-performance components.

Implementing AHB in Verilog

Implementing AHB in Verilog requires defining and implementing the various signals and registers of the AHB bus, including clock, reset, address, data, and control signals. Additionally, defining the interfaces and control logic for each device is essential to ensure proper communication with the AHB bus.

Here’s a brief overview of the steps involved in implementing AHB in Verilog:

| Step | Description |

|---|---|

| 1 | Define AHB bus signals and registers |

| 2 | Define interfaces and control logic for each device |

| 3 | Implement AHB bus signal detection and response logic |

| 4 | Consider data transfer order, priority, and error handling mechanisms |

LOCK Transmission in AHB

LOCK transmission is a control information initiated by the Master, indicating that the current transmission should not be interrupted or split. It is commonly used in multi-Master scenarios to ensure that a Slave responds to a Master’s LOCK transmission before responding to other Masters.

Here are some key points to remember about LOCK transmission:

- Master must use IDLE transmission to end LOCK transmission.

- LOCK transmission cannot cross Slave boundaries.

- LOCK transmission supports all Burst types.

- Most Slaves do not require support for LOCK transmission, as they typically execute each transfer instruction sequentially. However, in scenarios where multiple Masters access a single Slave simultaneously, support for LOCK transmission is necessary.

AHB Transmission Types

AHB supports various transmission types, including IDLE, BUSY, NONSEQ, and SEQ. Here’s a brief overview of these transmission types:

- IDLE: The Master indicates that no valid transaction is in progress.

- BUSY: The Master indicates that a valid transaction is in progress.

- NONSEQ: The Master indicates that the transaction is non-sequential, meaning that the next transaction will occur at a different address.

- SEQ: The Master indicates that the transaction is sequential, meaning that the next